Tracking System <—> Regulator System

State space에서 steady-state error가 0이 되지 않는 이유는 시스템의 구조적 특성과 제어 설계 방식에 있습니다. 아래에 자세히 설명드릴게요:

1. Control 방식의 한계:

- 주어진 제어 법칙 \( u = -Kx + r \)는 상태 \( x \)를 사용하여 피드백 제어를 수행하지만, **참조 입력 \( r \)**와의 직접적인 관계를 적절히 고려하지 않을 경우, steady-state error가 발생할 수 있습니다.

- 특히, 참조 입력이 step input(계단 입력)일 때, 시스템의 피드백 루프가 정확히 이를 추적하지 못할 가능성이 있습니다.

2. 극 배치(Pole Placement) 제어의 특성:

- 극 배치 제어 설계는 시스템의 **동적 응답(transient response)**를 개선하는 데 중점을 둡니다.

- 하지만 steady-state error를 자동으로 제거하는 기능은 포함되지 않을 수 있으며, 이를 추가적으로 보완해야 합니다.

3. 참조 입력과 시스템 모델의 불일치:

- 시스템에서 steady-state error를 없애기 위해서는 입력 신호 \( r \)와 시스템 출력 \( y \) 간의 차이를 줄여야 합니다.

- 시스템의 전달 함수 특성이 입력 \( r \)를 완벽히 추적할 수 없으면 error가 남습니다.

4. Integral Control (적분 제어) 부족:

- steady-state error를 제거하기 위해 제어 시스템에서 적분 제어기를 추가하는 경우가 많습니다.

- 적분 제어기는 steady-state에서 error를 누적하여 이를 보정하는 역할을 합니다. 하지만 적분 제어가 포함되지 않는 상태 공간 설계에서는 error를 줄이는 메커니즘이 부족할 수 있습니다.

해결 방안:

- 적분 제어기 추가: 적분 동작을 포함시켜 error를 누적하고 이를 보정하도록 설계합니다.

- 참조 상태 설계: \( r \)의 steady-state 값을 포함하여 상태 공간 모델을 수정함으로써, error를 최소화합니다.

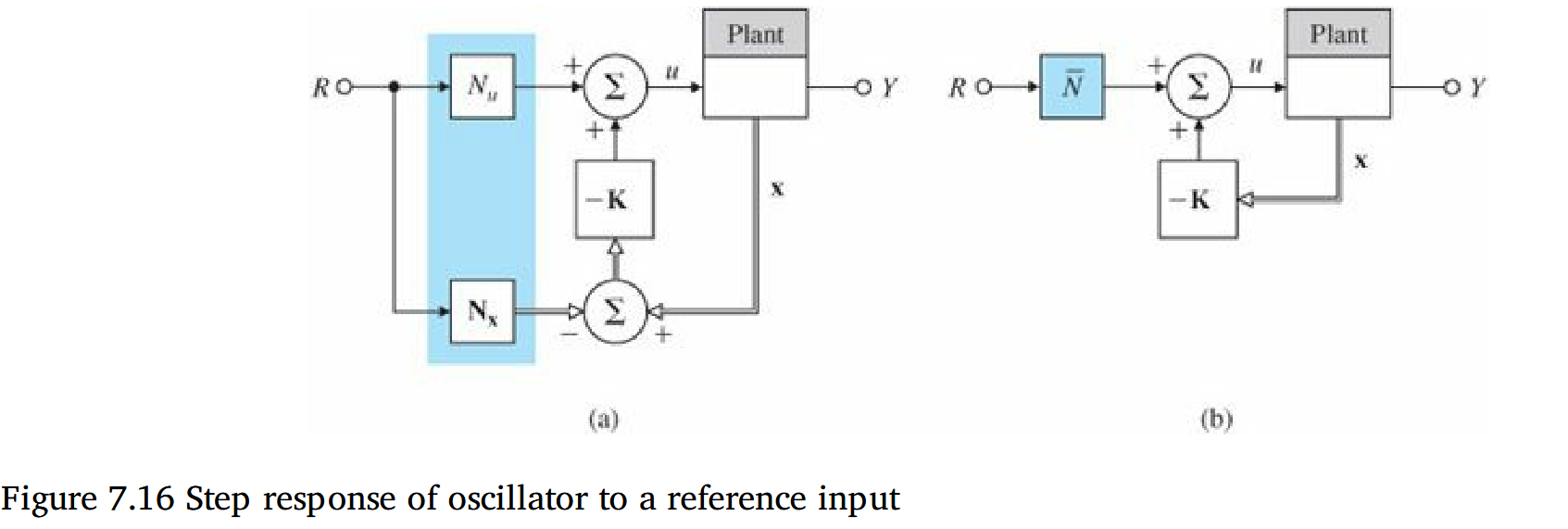

- 피드포워드 제어: 적절한 feedforward term을 설계하여 참조 입력과 시스템 출력 간의 차이를 직접 보완합니다.

결론적으로, state space 설계에서 steady-state error를 제거하려면 참조 입력을 고려한 추가적인 설계 요소를 포함해야 합니다. 더 궁금한 점이나 구체적인 상황이 있으면 알려주세요! ?